运算器实验

实验思路 是如何从头构建起这个电路并使其正常⼯作的

遇到的问题,如何解决。

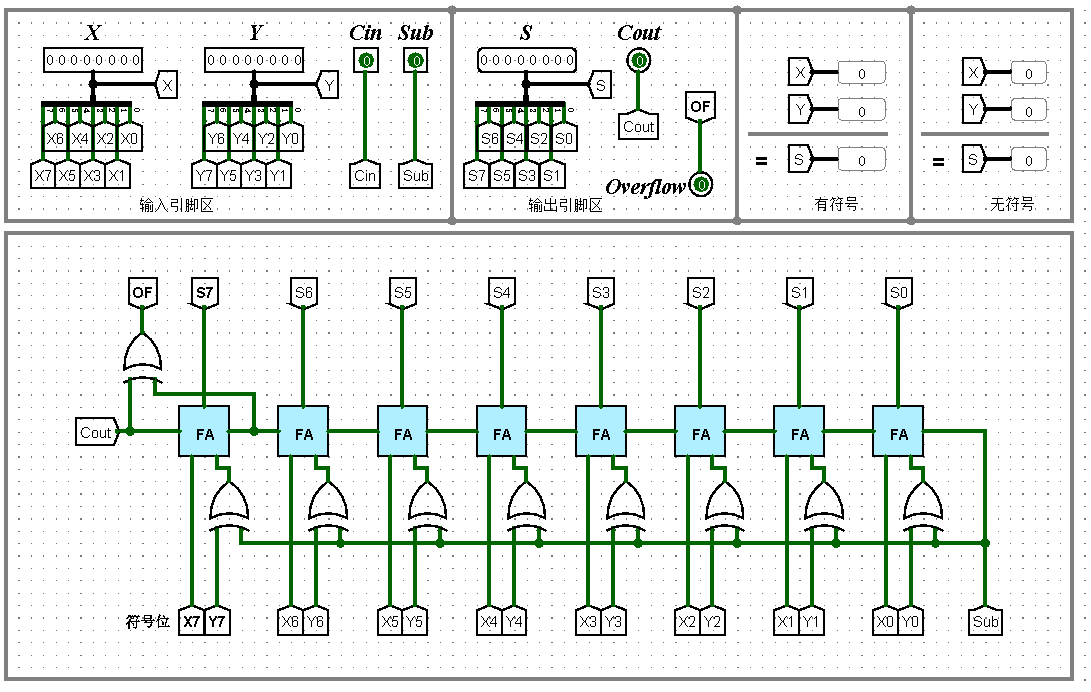

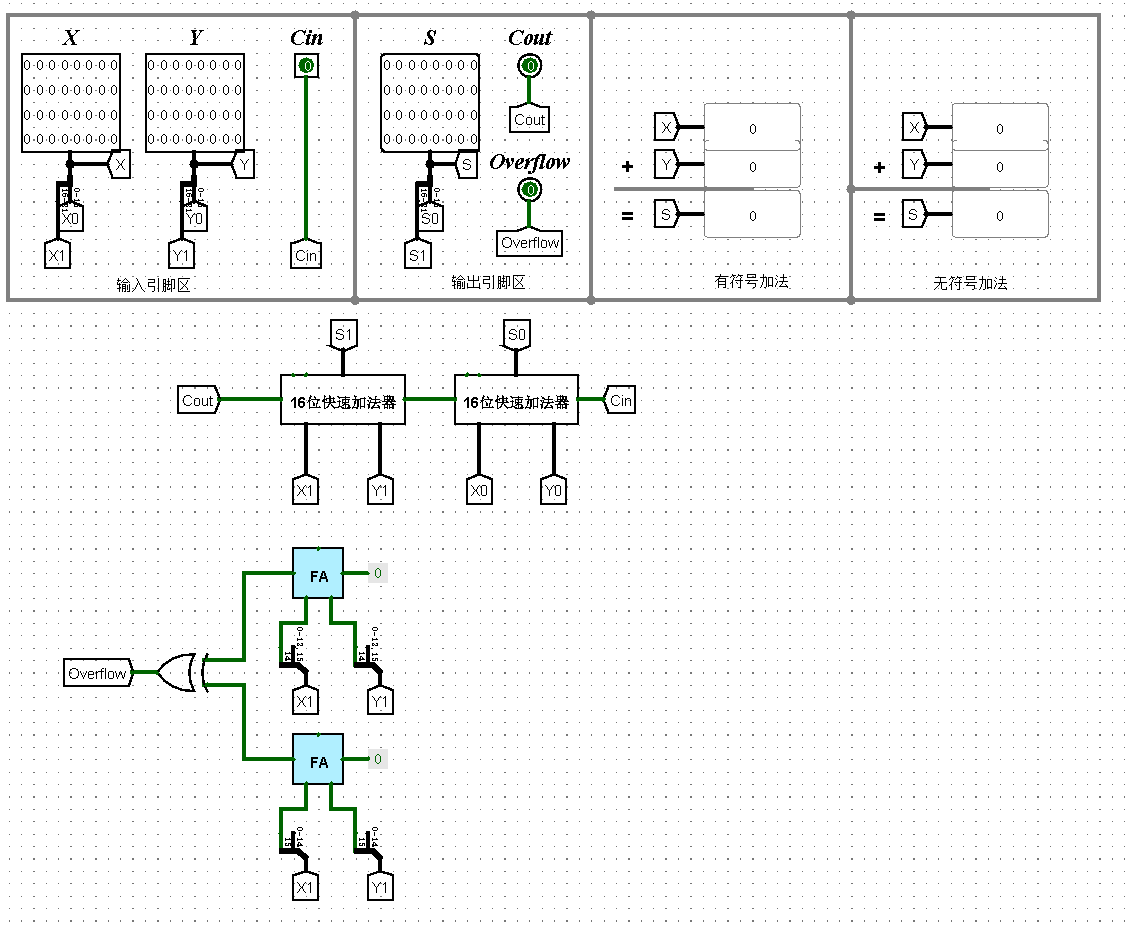

8 位串行可控加减法器

对于加减法的控制,你是采取何种⽅式实现的? 由于补码的性质,减法可以通过加法实现,只需将减数的补码再次求补送入加法器即可实现减法运算。因此,引入 Sub 信号,当 Sub 为 0 时,送入加法器的是 Y 本身,此时实现加法操作;当 Sub 为 1 时,通过异或门取反,送入加法器的是 Y 的反码,且 Sub 也送入了加法器最低位的进位输入,即对 Y 实现了取反加一的操作,完成了求补过程,从而完成减法操作。

你是怎样实现溢出检测的?其数学原理是什么?

利用最高数据位的进位与符号位的进位是否一致进行检测。

首先,只有两个符号位相同的数相加才可能发生溢出,那我们就可以根据操作数和运算结果的符号位是否一致进行判断。两个符号位为 0 的数,相加的结果符号位变成了 1 ,表示发生了溢出。同理,两个符号位为 1 的数,相加的结果符号位变成了 0 ,表示发生了溢出。

进而,也可以根据最高数据位的进位与符号位的进位是否一致进行检测,不同则为溢出。两个符号位为 0 的数,符号位进位则为 0 ,若此时最高数据位进位为 1,那最终的运算结果符号位就为 1,如前段所述,表明发生了溢出。两个符号位为 1 的数,符号位进位则为 1,若此时最高数据位进位为 0,那最终运算结果的符号位就为 0,如前,表明发生了溢出。

可以通过一个异或门来实现。

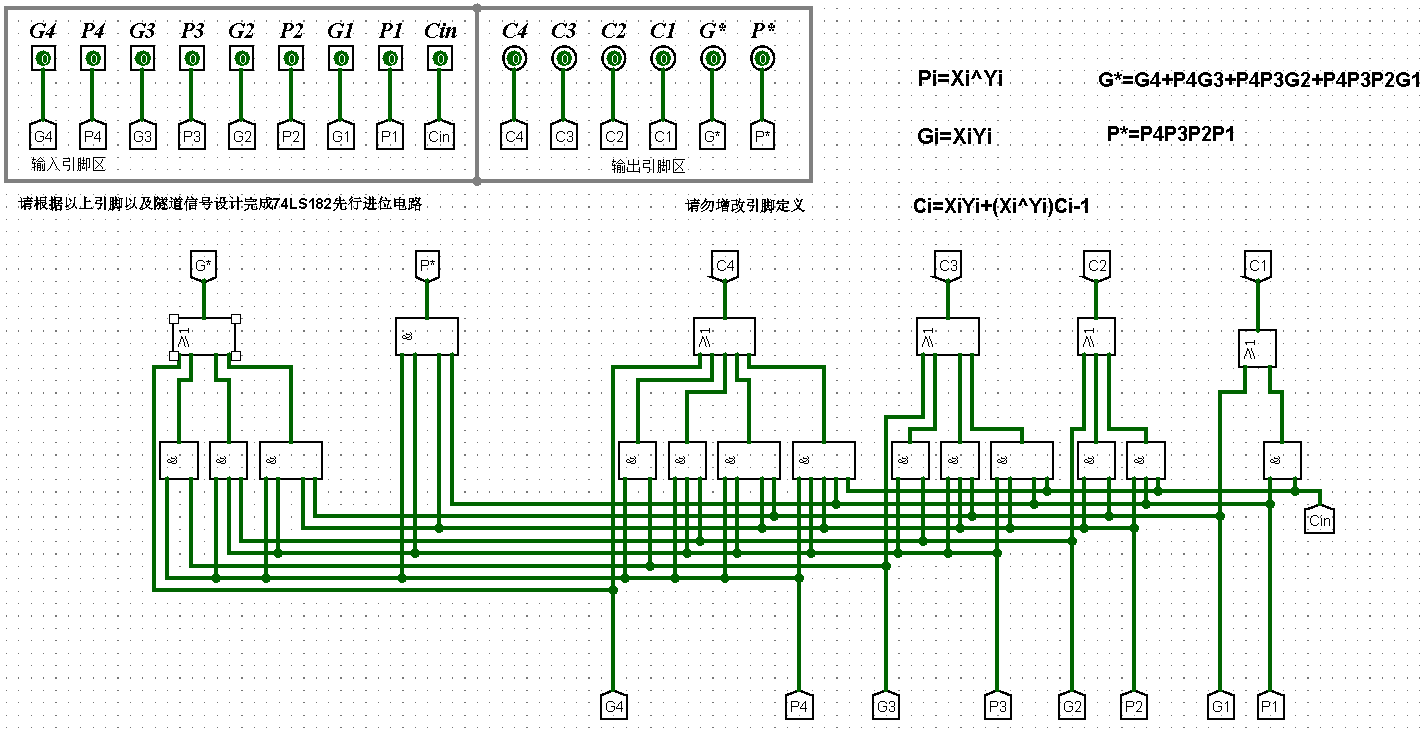

四位先行进位电路 CLA74182

CLA74182的作⽤是什么?

实现先行进位。提前得到所有全加器所需的进位信号。串行运算高位运算需要等待低位的运算。与串行加法器相比,可以提高运算速度。

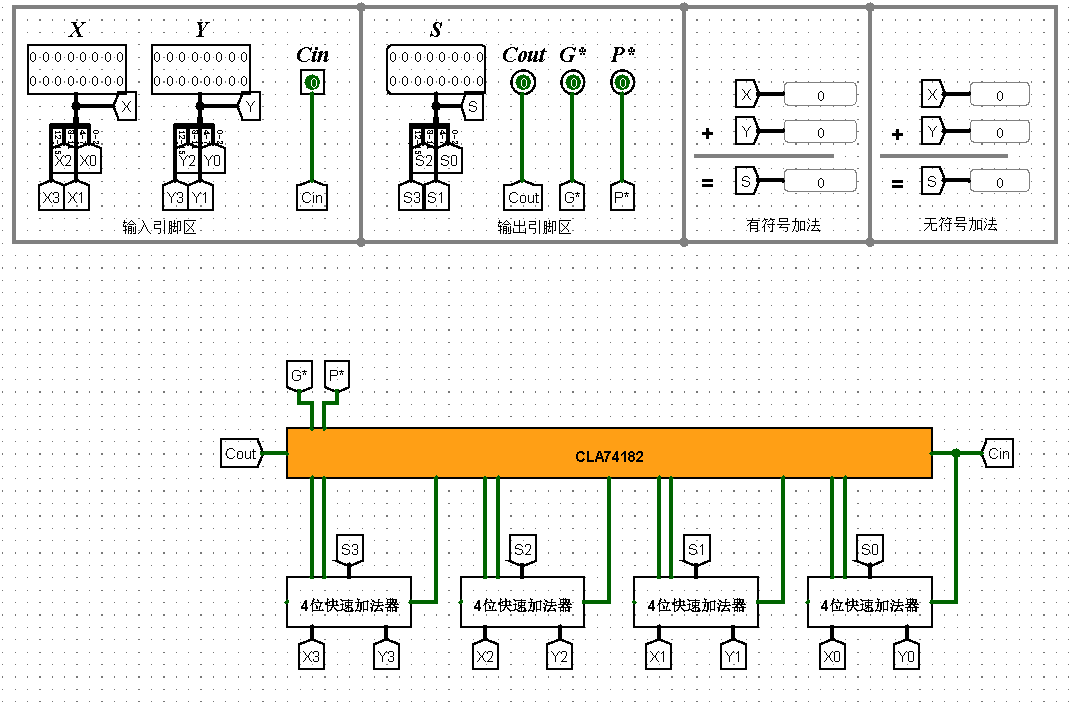

4 位快速加法器

快速加法器与普通的串⾏加法器的区别是什么?他是通过什么⽅法来实现“快速”的?

通过 CLA74182 提前得到所有全加器所需的进位信号。这样高位就不需要等待低位的进位数据,所有加法器可以并行运算,提高运算性能,实现“快速”。

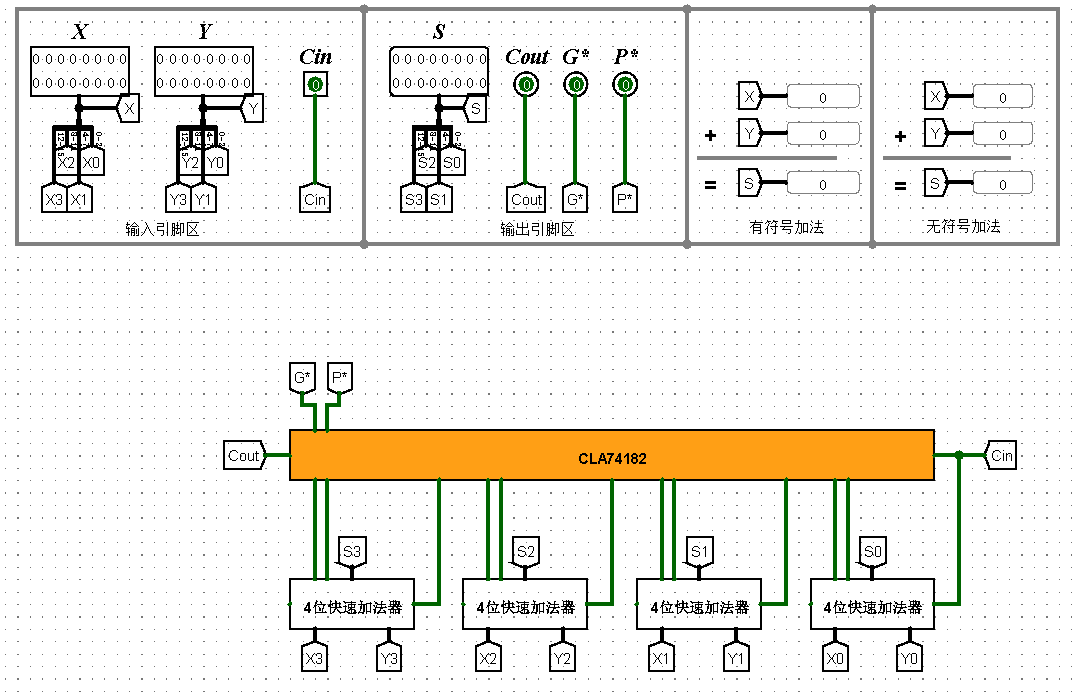

16 位快速加法器

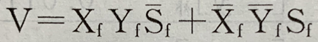

32 位快速加法器

你的溢出检测是如何实现的?这⾥是否可以选择其他的溢出检测⽅法?

根据最高数据位进位和符号位进位是否一致进行判断。

还可以选用根据操作数和运算结果的符号位是否一致来进行检测。

在有符号运算加法中,只有两个符号相同的数相加时才有可能产生溢出,因此,可以根据操作数与运算结果的符号位是否一致来进行检测

设Xf,Yf分别为两个操作数的符号位,Sf为结果的符号位,V为溢出标志位,V=1时即表示溢出,那么就有逻辑表达式:

这个逻辑表达式表明,有符号加法运算溢出的条件是:两个操作数都是正数结果却为负数,或者 两个运算数都是负数结果却是正数。

根据这个表达式,利用AND gate,OR gate,NOT gate可以容易地构造出相应的溢出检测电路。

实现此电路有哪些值得注意的地⽅?

可以有多种画图方式。

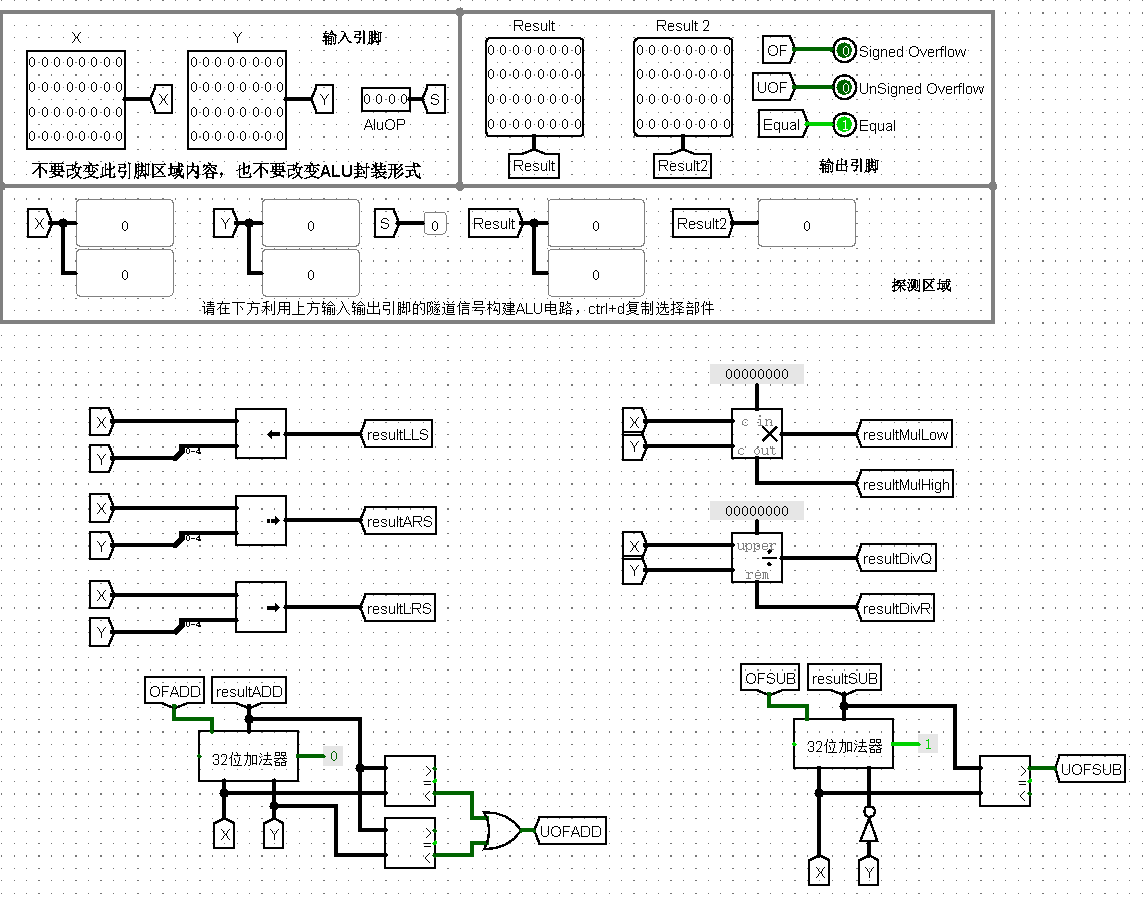

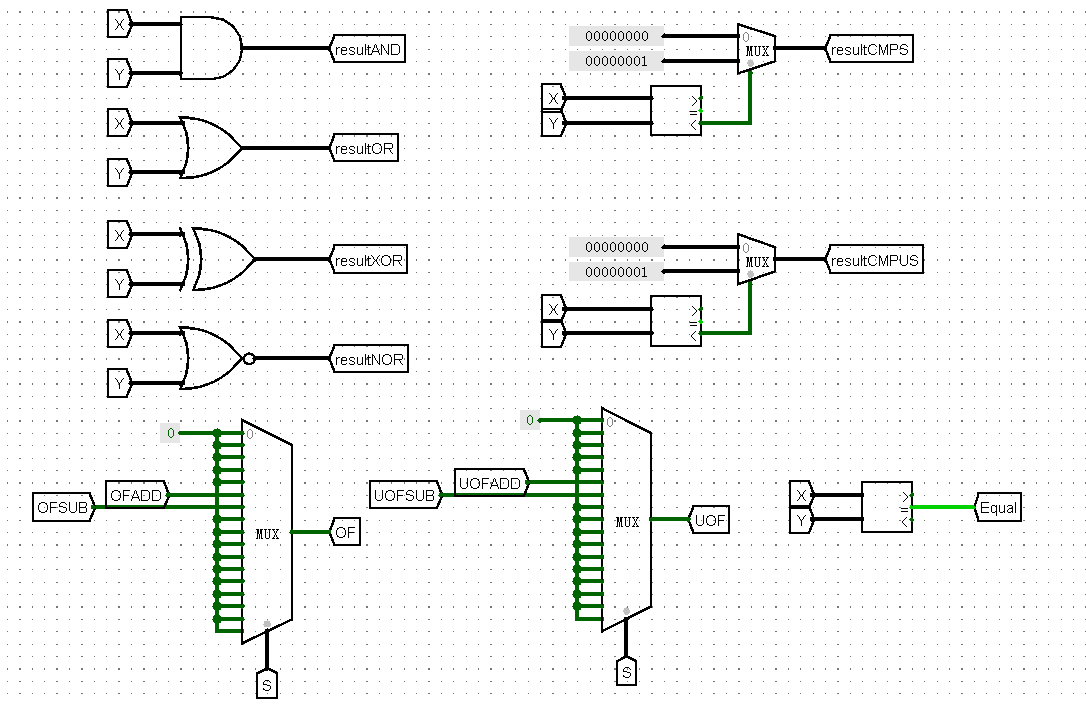

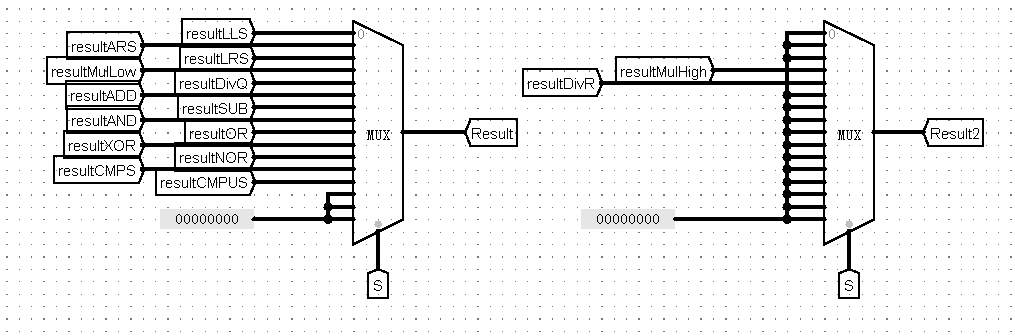

ALU

怎样实现功能选择?

通过数据选择器,选择作为输出的输入。

依次介绍各个功能的实现⽅式

逻辑左移通过 Logisim 自带的移位器,设置数据位宽为 32 位,移位类型为 逻辑左。

算术右移通过 Logisim 自带的移位器,设置数据位宽为 32 位,移位类型为 运算右。

逻辑右移通过 Logisim 自带的移位器,设置数据位宽为 32 位,移位类型为 逻辑右。

有符号乘通过自带的乘法器实现。

无符号除通过自带的除法器实现。

加法通过上面实现的 32 位快速加法器。

有符号加法溢出用 32 位的溢出直接连接。

有符号减法溢出用 32 位的溢出直接连接。

无符号加法溢出根据加数和小于加法来判断。

无符号减法溢出根据减法差大于被减数判断。

减法转化为加法,对 Y 用一个非门先取反,Cin 输入 1,即再加一,得到补码。

按位与、按位或、按位异或、按位或非用自带的逻辑门实现。

符号比较通过比较器实现,设置数字类型为关于 2 的补码。

无符号比较通过比较器实现,设置数字类型为无符号。

Equal 比较器实现。

重点介绍OF,UOF,加法,减法

运⾏运算器测试电路检测

存储器实验

结合⾃⼰实现的电路回答后⾯列出的问题

对于⽤到的重要器件不能⼀句带过,需要解释其在电路中的作⽤以及不同情景下的表现⾏为

提出⾃⼰在实验中碰到的问题以及如何解决的(加分项)

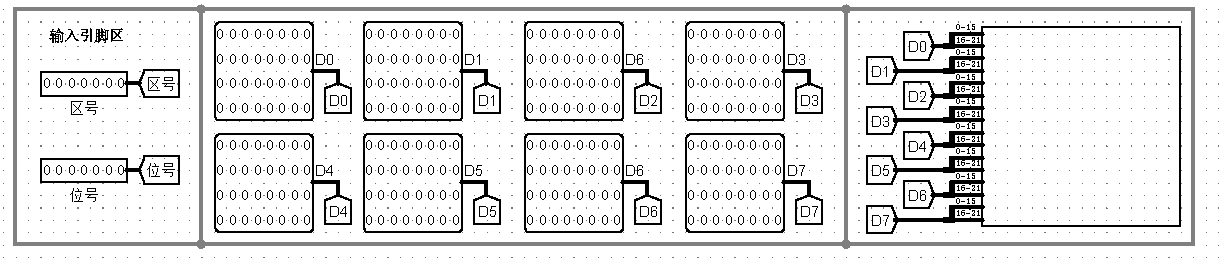

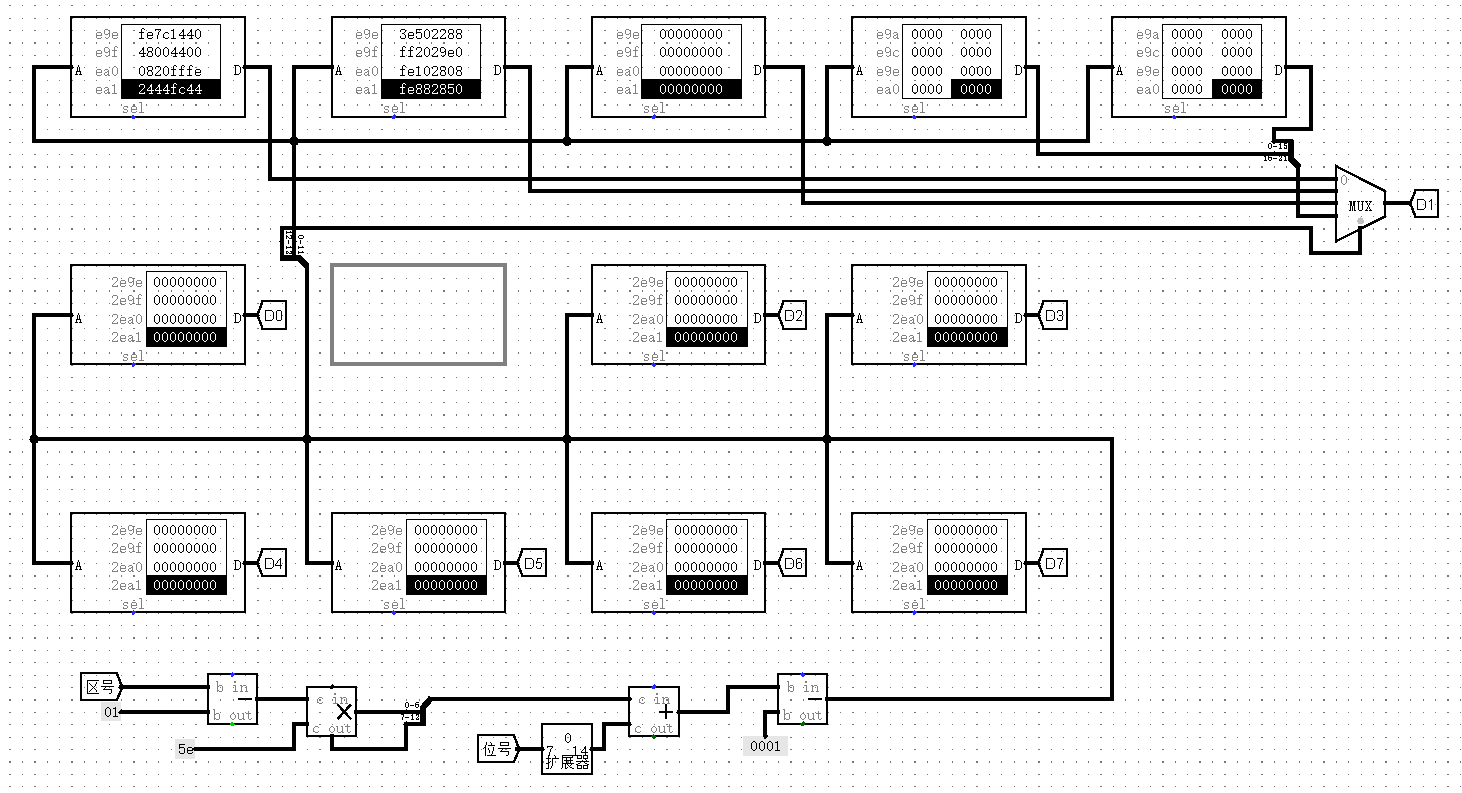

存储扩展

简要介绍 该电路的作⽤,以及各个引脚的含义

根据输入的区号和位号,得到对应的汉字字形码,即D0 和 D7共 256 位数据。

D0 - D7 每个对应字形码的 32 位。

为什么该实验需要进⾏存储扩展?

数据线是 32 位,所以两个 4K*16 位的芯片需要进行位扩展。

地址线是 14 位,所以 4K*32 位的芯片要进行字扩展。

实验中存储器数据和 LED 点阵码是如何对应的?

一位对应 LED 点阵上的一个点。

详细介绍 实验中存储器扩展的基本思路以及具体实现

两个 4K*16 位存储芯片先进行位扩展得到 4K*32位的芯片,然后再和其余 3 个 4K*32 位的芯片进行字扩展得到 16K*32 位的芯片。

具体实现通过 分离器 将 16 位芯片的输出数据组合再一起,实现位扩展。

通过解码器得到片选信号选择具体芯片对应地址的数据。

对于该实验,在进⾏字位扩展过程中需要注意什么?(提⽰:地址空间)

对于电路图中的3个4K32位ROM和2个4K16位ROM,由于数据已经导入到ROM中,所以顺序固定为从左到右地址增加,即在进行字扩展时,注意地址区间的划分。也就是左边第一个芯片连到输出 0。

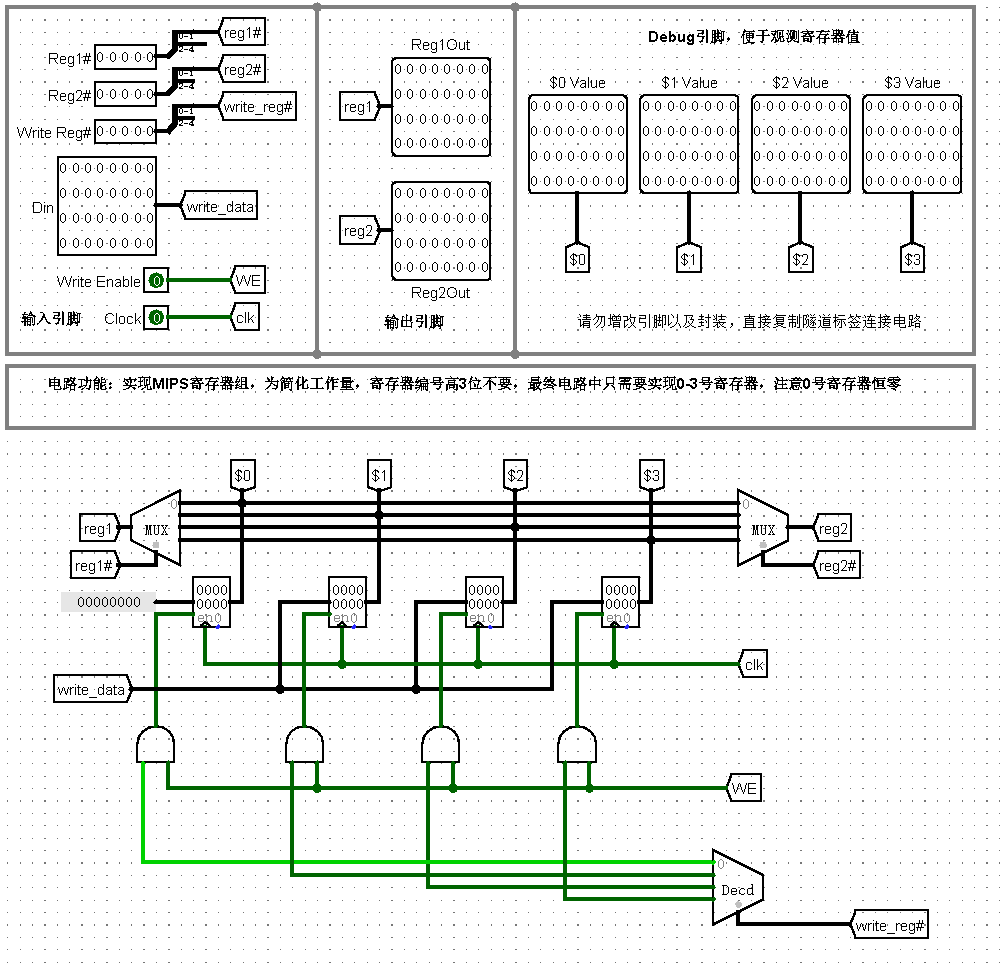

寄存器文件设计

简要介绍

该电路的作⽤,以及各个引脚的含义

实现 MIPS 的寄存器组,包含 4 个寄存器。

-分别通过reg1# reg2# write_reg#获得输入的三个寄存器编号,因为实验只要求实现0-3号寄存器,所以只需提取5位编号输入的低2位(00/01/10/11)

-通过 write_data 获取要写入寄存器的32位数据

-通过 WE 获取写入标志

-通过 clk 获取时钟信号

-将读寄存器1的值输出到 reg1

-将读寄存器2的值输出到 reg2

-将4个寄存器当前保存的值输出到 $0 $1 $2 $3,用于观测。

详细介绍

如何实现寄存器选择输出?

用数据选择器把四个寄存器的数据输出端口作为输入,reg1接到数据选择器的输出端口,reg1# 控制数据选择器选择作为输出的输入。

如何实现寄存器选择写⼊?

将寄存器的使能端连到解码器上,write_reg# 信号控制解码器的哪个输出为 1。解码器输出再与 WE 信号相与。当解码器输出为 1 且 WE 信号为 1 时,将 write_data 中的数据写到 寄存器中。 第一个寄存器输入数据端口连接 常量 0,实现 0 号寄存器恒零。